Proceedings of the First Workshop on Productivity and Performance in High-End Computing (PPHEC-04)

# February 14, 2004 Madrid, Spain

Held in conjunction with the Tenth International Symposium on High Performance Computer Architecture

# **Program Chair:**

Ram Rajamony, IBM Research

# **Program Committee:**

Victor Basili, University of Maryland at College Park James Browne, University of Texas Austin John Carter, University of Utah John Grosh, OSD Mary Hall, USC Information Sciences Institute Jeremy Kepner, MIT Lincoln Labs Karthick Rajamani, IBM Research Ram Rajamony, IBM Research Marc Snir, University of Illinois at Urbana-Champaign

# 1<sup>st</sup> Workshop on Productivity and Performance in High-End Computing Febryary 14, 2004 Madrid, Spain

| Morning Keynote: The Coming Crisis in Computational Science                                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Application Development Productivity Challenges for High-End Computing                                                                               |

| Comparing Network Processor Programming Environments: A Case Study                                                                                   |

| Templating Transformations for Bitstream Programs                                                                                                    |

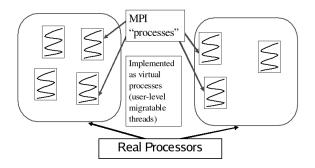

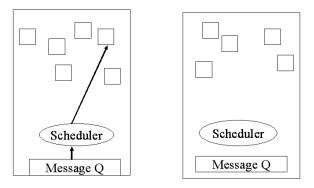

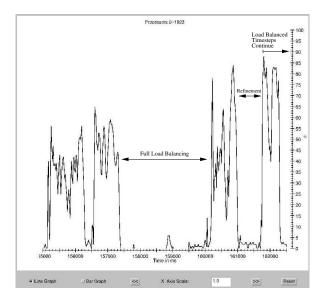

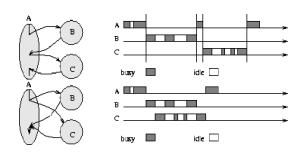

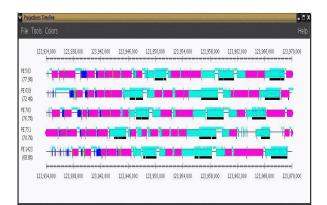

| Performance and Productivity in Parallel Programming via Processor Virtualization                                                                    |

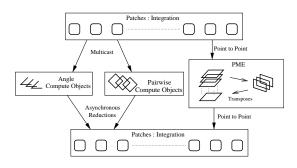

| Afternoon Keynote: Building High Performance Scientific Applications for<br>Parallel and Distributed Systems using a Software Component Architecture |

| Introducing the "Application Kernel Matrix"                                                                                                          |

| Managing Complexity in Modern High End Scientific Computing through<br>Component-Based Software Engineering                                          |

| The High-Level Parallel Language ZPL Improves Productivity and Performance                                                                           |

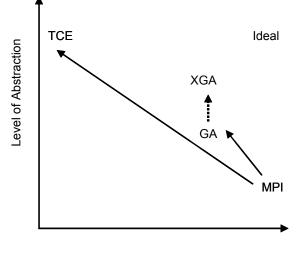

| Raising the Level of Programming Abstraction in Scalable Programming Models                                                                          |

Proceedings of the First Workshop on Productivity and Performance in High-End Computing (PPHEC-04)

# Morning Keynote

The Coming Crisis in Computational Science

Douglass E. Post Los Alamos National Laboratory

# The Coming Crisis in Computational Science

Douglass E. Post

Los Alamos National Laboratory, Los Alamos, NM 87544 post@lanl.gov

#### Abstract

The enormous increase in computing power over the last forty years has opened up new opportunities to analyze and solve important problems that face society. Computer simulations and analysis have unprecedented potential to address complex, non-linear phenomena with realistic data and geometries. Modern scientific research, originally grounded in experiment and its theoretical interpretation, is becoming a triad of experiment, theory and computation. Computer simulations and analysis are beginning to be used for engineering design and public and private policy decisions. Yet computational science is not nearly as mature as the traditional methodologies and is undergoing "growing pains". This is not surprising as history indicates that it takes time, and quite a few major and possibly dramatic mistakes, for a methodology to mature. These major mistakes are beginning to occur. The computational science community needs to analyze these mistakes and learn from them if it is to succeed.

#### 1. Introduction

Computational science-the use of large scale computers to address and solve important technical problems-is becoming an everyday tool for design and analysis of complex technical issues. Applications include scientific research, engineering design, policy analysis, training and emergency response and environmental analyses. Computational science has the potential to address complex issues with a degree of realism that has heretofore only been imagined. This exciting and very important-indeed revolutionary-potential is due to the enormous growth in computer power (speed and memory) over the last 50 years. This growth shows no sign of slowing in the near term. Yet computational science is a very new and immature discipline. It has not achieved the level of maturity of traditional methodologies such as experiment, theory, engineering design and conventional policy analysis for solving problems.

For example, when a scientist receives a computational science paper from a journal to referee, he has no definitive way to determine if the paper is correct. He cannot reproduce the results in the paper, and generally he can't check the important results with experimental data. The most important results typically make predictions for situations for which there is no data. That's often the purpose of the calculation, after all. Even if he had a listing of the code – the referee usually doesn't – that is not enough to determine the validity of a very complex and large calculation. All that he can do is to subject it to a series of "plausibility" checks. Is the paper consistent with known physical laws? Is the author a reputable scientist, known for careful work? Are the results consistent with other work in the field? Is the code validated with data as close as possible the regimes of application? Do the computational methods seem sound and applicable to the problem? Are the original model and the fundamental equations correct? These criteria are not nearly as reliable as the criteria used for theoretical or experimental papers. A reviewer can re-derive the important formulae in a theoretical paper. Experimental science is a well-established methodology, and important experiments are duplicated fairly quickly. In fact, important experimental results are usually not accepted by the general scientific community until they are confirmed by independent experiments. "Discoveries" like cold fusion have their moment of fame then fade into infamy as "irreproducible" results. Reproducibility is a cornerstone of sound science.

In addition, these criteria discriminate against the reporting of new and exciting results, since such results usually cannot be thoroughly checked, and are probably, but not always, wrong. Major new contributions are thus less likely to survive the refereeing process in favor of more modest extensions of previously accepted work.

Many things could be wrong with the computational science paper that the referee could not detect. The code could have errors in the way it was written such as bugs, the wrong use of computer or mathematical algorithms, inadequate resolution in time or space, unconverged solutions, etc. Even if the code had few errors, the models and equations in the code could be inadequate or wrong. As Robert Laughlin points out, "One generally can't get the right answer with the wrong equations." [1] The physical data used in the code may not have adequate resolution or may be inaccurate. The scientist or engineer running the code may not know how to set up or run the problem correctly. He may not know how to interpret the results of the code accurately. Yet referees are expected to judge the correctness of the paper. It's a challenge the community needs to address.

Even more importantly, significant scientific, engineering design and public policy questions are beginning to be decided on the basis of computational science results. As a community, it is our responsibility to ensure that computational science achieves the same level of reliability as theoretical and experimental science and engineering design. Otherwise computational science will not be a credible methodology, and its potential for contributing to the betterment of the human condition will not be realized. If a significant number computer predictions and analysis are wrong, and there is no way to determine which ones are right and which are wrong, people will not rely on them and will not support the development of the field.

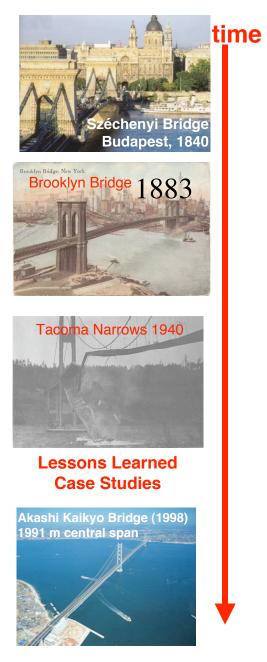

In "Design Paradigms", Henry Petroski traces the roughly four steps needed for an engineering technology to reach maturity[2]. Among his examples is suspension bridges (Figure 1). The first step involves the design and construction of the first suspension bridges. The designers and construction crews did not know the design limits. The designs therefore were very conservative and extensively over-engineered. Although there are often initial failures, the designers generally got it right fairly quickly. An example is the Széchenyi chain bridge over the Danube joining Buda and Pest constructed in 1840. It was stood for 105 years until the Germans destroyed it in World War II. It was rebuilt in the 1990's and stands today. The second step involves cautious design improvement and optimization. An example is the Brooklyn Bridge constructed in 1880 by John and Washington Roebling. It is still standing and carrying a modern traffic load after over 120 years. The third step involves the development of continually more ambitious designs that push the limits of the existing technologies until failures occur. The cautious approaches and the deep fear of failure of the prior generations of designers are often forgotten in the enthusiasm to go beyond the achievements of the past. The Tacoma Narrows bridge, constructed in 1940 failed catastrophically due to the excitation of harmonic oscillations driven by wind. Such bridge failures are spectacular. Almost everyone who reads this paper has seen the short movie of the galloping Tacoma Bridge as it bucked and moved in the wind until it

collapsed into the river. The civil engineering community studied and analyzed the causes for the failures, then developed solutions that became part of the design methodology for all future suspension bridges. This fourth step leads to a mature field based on the development and adoption of the "lessons learned" from the failures and successes. Now very large suspension bridges are being built such as the 1991 m span Akashi Kaikyo Bridge in 1998.

Figure 1 History of Suspension Bridges[2].

Computational science is in the midst of the third step on the path to maturity. The first generation of computational science involved the use of the supercomputers of the 1950's, 1960's and 1970's. The authors of these applications used the codes to analyze data, design nuclear weapons, model supernovae, conduct engineering analyses, etc. Computational science was a new field and everyone was very aware that it had limitations. Due to restrictions in memory and processing speed, the problems generally did not have adequate spatial or temporal resolution and the solutions were often not converged. Many times only very approximate models were employed for the problems being addressed. Nonetheless, computational tools were a step forward, and-used with caution and carefully verification and validation-produced better answers than could be obtained with traditional analytic techniques. As computers became more powerful, the DOE and the NSF established "supercomputer" centers in the US to provide supercomputer capability to the academic and general national laboratory community. The DoD used supercomputers to address important national security issues. Industries such as Boeing and General Motors used supercomputers for engineering analyses of aircraft, engine and structural automobile components. There was still generally a strong component of skepticism about computational results and as a consequence, computational predictions were thoroughly checked and validated.

By the 1990's, computing power had reached the point where many of the prior limitations on resolution and ability to solve complex mathematical systems had been overcome. Computational techniques began to really have the potential to address difficult and important problems such as climate change and weather prediction, nuclear weapons design, astrophysics, non-linear turbulence, chemistry, biology and human event simulation. This coincided with the advent of a new generation of scientists and engineers who were specifically trained as computational scientists. They began to use computational techniques to tackle many very difficult and complex problems. While these scientists and engineers were highly skilled at using computers, many did not have the inherent skepticism about computational results that was characteristic of prior generations. Although they knew that computational models are only an incomplete model of nature, they have sometimes placed an unwarranted faith in the validity of the computational results.

There are many examples of computational analyses and results that were important elements of a policy or design decision, but were later determined to have been inadequate or seriously flawed. Among these, in my talk I will discuss some examples in enough detail to illustrate the main elements of a "lessons learned' exercise. One candidate example involves an assessment of potential failure modes of a large engineering system. The assessment indicated that there was sufficient margin against failure. However, the system failed resulting in destruction of the system and loss of life. Further analysis after the failure indicated that the computational analysis procedure was seriously flawed, leading to a false sense of confidence in the reliability of the system.

The second assessment involved the use of computer modeling to "explain" a new and very exciting, but very surprising, experimental discovery. A computer simulation was able to "reproduce" the experimental result by changing the boundary conditions much more than was reasonable based on the physics of the problem. By treating the boundary conditions as "free parameters", the simulation could "reproduce" the experimental results. With this confirmation, the authors published their results. The publication caused a great deal of excitement. Many groups began to repeat the experiment, but none were able to achieve the results reported in the paper. The original experimental group brought in a second group from their laboratory to repeat the measurement, and the second group found a null result. The original analysis of the experimental data was determined to have been flawed, and the result was withdrawn. All of this might have been avoided had the computer simulation group not treated important physics constraints as "free parameters". The simulation could have served to alert the experimental team that their results were not correct, but instead it gave them false confidence in their results.

Another example involved a theoretical prediction of the performance of a proposed new facility. Based on extensive analysis of the results of smaller facilities by the international community in a particular field, it had been proposed to build a large experiment. Just as the design of the large experiment was being completed by an international team, a small group of three theorists completed a computer simulation based on a new code of the expected performance of the proposed facility. Their initial results indicated that the performance would be poor due to instabilities and that the proposed facility would not be able to achieve its goals. Their results were widely distributed in the popular media, and contributed strongly to several partners withdrawing from the project. Extensive analysis by the international community led to the realization that the three theorists had left out important effects that stabilized the instabilities, and that the expected performance would be roughly what the original design team had predicted. In this case, a computational prediction that was later proven to be

wrong had an important impact on a scientific policy issue.

There are many other examples that are also available. These examples illustrate that the computational science results are beginning to play an important role in society, but not always a positive role. If this role is to be a positive one, we, as a community, must work to achieve the level of maturity for which our results are accurate and reliable. As in the case of suspension bridges, we must start analyzing our failures and successes, and learn from them. To illustrate some of the kinds of "lessons learned" analyses we will need to conduct, I describe an exercise that Richard Kendall and I carried out for six computer simulation projects in the nuclear weapons program[3]. The analysis we carried out emphasizes the code development process more than the validity of the results of the computations, but reliable answers requires a mature methodology for development of the analysis tools.

#### 2. "Lessons Learned from ASCI"

Richard Kendall and I developed a set of "lessons learned" from the US Department of Energy's Accelerated Strategic Computing Initiative (ASCI) program[3]. Since 1996, the ASCI program has spent over \$3B to develop the predictive nuclear weapons simulation capability required for certification of the stockpile without nuclear testing. The ASCI program has elements that focus on the development of large scale, massively parallel computer platforms, the associated operating systems and code development tools, application codes and supporting algorithms and models. Some of the applications development ASCI projects have been successful in meeting their objectives and some have not. We analyzed the application projects at the Lawrence Livermore National Laboratory (LLNL) and the Los Alamos National Laboratory (LANL) utilizing metrics and case studies that focused on the history, organization and institutional support of the code projects. By identifying the common elements that led to success or failure to achieve objectives and comparing them to the experience of the information technology (IT) community (e.g. [4]), we developed a set of recommended practices for largescale technical code projects (Table 1).

Table 1: Code Development "Lessons Learned" from theASCI Program at LANL and LLNL

- 1. Build on the successful code development history and prototypes for your organization.

- 2. Good people in a good team are essential for successful code development projects.

- 3.Software Project Management: Run the code project like a project.

- 4.Risk identification, management and mitigation are essential for successful code development.

- 5 Determine the schedule and resources from the requirements (goals and objectives, quality, team building and survival, and added value), not independently.

- 6. A strong customer focus is essential for success.

- 7.Better physics in a physics code is much more important than better computer science.

- 8. Use modern but proven Computer Science techniques; do not let your project become a Computer Science research project unless it is one.

- 9 Train the teams in project management, code development techniques and the physics and numerical techniques used in the code

- 10. Software Quality Engineering: Use Best Practices to improve quality rather than processes.

- 11. Validation and Verification of codes are essential.

While the "lessons learned" list may seem obvious and certainly contains no surprises, every code project we studied violated at least a few. Almost all were violated for the least successful projects. These lessons are generally not new. Indeed, many of these lessons can be found in Fred Brooks' 1975 classic: "The Mythical Mon-Month" [5]. Also, these principles apply to many other organized human activity[6].

1. Identify the things your organization or institution does well and build on them. Introduce change with clearly defined goals in an evolutionary fashion. Even though you may think that the ideal structure for effective code development might be radically different from the existing organization and culture, radical, instant changes will disrupt whatever is working, and likely will not lead to success. Successful change takes time and requires that the people in the institution feel "safe" and trust the management to treat them fairly.

2. Teams, not organizations or processes, develop software. Form the best team you can, support it, and help it "jell." A good team is the strongest asset an institution can have. Developing good teams is the key to developing good software. A good team is also a crucial deliverable for a successful project because any further progress must build on the team.

3. Run the code project like the project that it is, with requirements, deliverables, a sound plan, realistic schedules and adequate resources. Align authority with responsibility. The project manager must be able to control the resources and the team, and have the active support of senior management. Otherwise, he is a project "cheerleader," not a project leader, and the project will fail.

4. The development of large, complex technical codes is inherently very risky. Many, if not most, development efforts fail to meet their initial objectives, and quite a number fail completely. Identifying the major risks, minimizing them and providing contingency and mitigation is essential. The major risk factors for software projects are [7]:

- uncertain goals, objectives and requirements;

- inadequate resources and support, including an overly ambitious schedule;

- institutional turmoil, including too much employee turnover;

- requirements and goals that change too rapidly or increase too fast; and

- poor team performance.

Poor team performance is the smallest risk factor for the ASCI code projects [3] and for the general software industry [7]. The other risk factors strongly dominate. Most code project failures (for ASCI as well as the general IT community—[4, 7]) are due to the failure of senior management to fulfill its responsibility to provide guidance and support for the code projects. The ASCI projects, and most technically oriented code development efforts, have additional risks because they must develop new algorithms and rely on other projects and groups to provide essential components.

5. If adequate resources and schedule are not provided, the project will fail to meet its objectives on time. This is a failure itself and may initiate a chain of events that will cause it to fail altogether. There is even less flexibility for software development than for conventional projects where one can fix two, but not three of objectives, resources and schedule. For software, one can only fix the objectives. The *objectives and goals* determine the *resources* and *schedule*. The rate limiting process for code development is the rate at which people can analyze problems and develop solutions. The ability to increase the schedule is severely limited. Similarly, the maximum size of a code team is limited by the ability of people to communicate complicated information with each other. This is reflected in the quantitative analysis that follows in the next section. The standard estimation techniques indicate that the optimal schedule and team size are a function only of the size and complexity of the code[8]. Frederick Brooks put it another way: "Adding more staff to a late project will only make it later."[5] Ed Yourdon wrote a book entitled "Death March" about the disastrous consequences of overly ambitious code project schedules[9].

6. Codes that customers do not want to use are like experiments that do not take data or equipment that people do not use. Such codes are a waste of resources and the efforts of creative people. The code team and management must focus on providing what the customer both *needs* and *wants*. If the customer does not want or like the product, the code will fail even if it is what he really needs.

7. The value of the code to the ASCI customer is the physics capability of the code. The degree of innovative computer science in the code is of little interest to him. The most successful ASCI codes have concentrated on

improved physics and have been very conservative in their use of cutting edge computer science.

8. Similarly, computer science research within the context of an application project greatly adds to the risks and often results in code project failure. Use modern, but proven techniques. Improving the physics is risky enough. Leave computer science experiments to those who can afford to fail a few times.

9. Invest in your people through training and professional development. They will become more capable as they acquire new skills and will be more productive. It is a good way to encourage change and to get the team members to see how other groups and industries tackle their problems. In addition, their morale will increase in proportion to the support of their management. Training also provides an opportunity for code team members to share experiences with the rest of the team and with other teams.

10. Software quality is important. However, researchoriented staff are not going to take a series of processes defined in a book and follow them blindly because someone in authority tells them to. They will apply the same standard to software development methods that they apply to their science. They have to be convinced that it is right and adds value to their work. It is more successful to convince the teams that individual practices add value (configuration management, etc.) than to try to convince them that a large system of processes is something they should blindly embrace on faith.

11. Physics codes are an incomplete representation of reality. The models have shortcomings and often have mistakes in their implementation. Without a verification and validation program for the codes and their applications, there is no reason to believe that the code results have any validity at all.

The software quality issue is important. If poor quality codes are being produced, the sponsors and customers will take action. Already the DoD and other customers have developed fairly rigid processes for code development and software quality assurance in response to disastrous results due to poor quality software aircraft and satellite control software. The Air Force cannot tolerate bugs in aircraft control software that result in plane crashes. They have established a very rigorous procedure for vendors to follow to develop such software[10]. An analogous situation existed in the automobile industry in the 1970's and 1980's. The American automobile was producing poor quality cars and people were beginning to stop buying them. The Japanese were building cars that had high quality and people were buying them. A basic difference was that the US automobile industry did not sufficiently emphasize quality on the assembly line and in components. They tested the cars after they came off the assembly line and fixed the worst ones. The Japanese, on the other hand, emphasized quality at every step of the assembly process and for components. They tested the cars at many points of the assembly and tested the components before installation. The net result was that far fewer cars with poor quality emerged from the assembly line, and got into the hands of consumers. The value of software quality assurance is likely to be maximized when it is applied at all steps of the software development process, rather than just at the end. However, just as in the assembly line, different development processes require different methods, no one size fits all. Also, just as the Japanese emphasized input from the assembly floor, the code developers themselves are often the best judges of how to implement quality. A process blindly imposed from above will likely get the same type of malicious compliance observed in the US auto industry.

#### 3. Quantitative Estimation

The above lessons learned were based on a qualitative and a quantitative analysis of the history of the different code projects and comparison with the information technology industry and conventional project management and scientific research. The quantitative analysis was a key element in establishing that the ASCI code projects had not been given a consistent set of requirements, resources and schedules. Our analysis [3] was relatively simple compared to the methods often employed in the Information Technology community[11], but was nonetheless revealing. We analyzed simplified case studies for many of the DOE's Accelerated Strategic Computing Initiative (ASCI) code projects to identify the key factors that determine the success or failure of complex scientific code projects. We found that the key predictor was the age of the code project and the amount of time allocated to complete the project and meet milestones. Our analysis of the historical data indicated that it takes about 8 years to develop an ASCI weapons code. The projects that had 8 years of development often succeeded, and those that did not have 8 years of development all failed to meet their initial milestones. This result emphasized the crucial need for a consistent set of requirements, resources and schedule.

The case studies included metrics (code size, team size, age, etc.). To see if the ASCI experience is consistent with the Information Technology (IT) community, we analyzed the case studies using a generic "function point" model [11] widely used by the IT industry. We calibrated this model for scientific code projects using the ASCI case study data. Function points are a weighted total of inputs, outputs, inquiries, logical files and interfaces [11, 12]. Functions Points were not developed for technical software, but were the best measure we could find.

$$FP = \left(\frac{C + + SLOC}{53} + \frac{C SLOC}{128} + \frac{F77 SLOC}{107}\right) \quad (eq. \ 1)$$

Schedule(months) =

$$FP^x$$

0.4 < x < 0.5; use x = .47 (eq. 2)

Team  $Size = \frac{FP}{150}$  (eq. 3)

We first converted the single lines of code to Function Points (FP)(e.g. eq. 1). T. Capers Jones lists the equivalent single lines of code (SLOC) per function point (FP) for the common computer languages [11]since computer languages have different information densities.

#### Schedule = Contingency x Function Point schedule + Delays (equ. 4)

In this model, the required schedule and average team size are determined by the Function Point (FP) count (eqs. 2,3). We calibrated and modified these general scalings to account for the added complexity and viscosity associated with developing scientific codes

$$Team \quad Size = 3 + \frac{FP}{150} \bullet 0.6 \qquad (eq. 5)$$

specifically for the nuclear weapons complex. We increased the schedule by 1.5 years to account for the additional time it takes to recruit, hire, train and get security clearances for code development staff. Using a methodology developed by the Lawrence Livermore National Laboratory Engineering Department[13], we calculated a contingency factor of 1.6 to account for the additional risks, uncertainties, complexities, etc. for the LANL and LLNL computing environments. We modified the standard FP scaling for the size of the code team (eq. 5)[11] to match the ASCI data. We included a correction for small code teams.

We analyzed seven code projects, three at LLNL and four at LANL (Table 2). For security reasons, we have identified the LLNL codes with the letters A, B and C. Table 2 lists the size of the code in function points, the time estimated by equation 4 to develop the initial capability of the code project, the actual age of the code at the point it was expected to accomplish its first milestone, whether or not the project succeeded, the optimal code team size estimated from equation 3 and the actual size of the team.

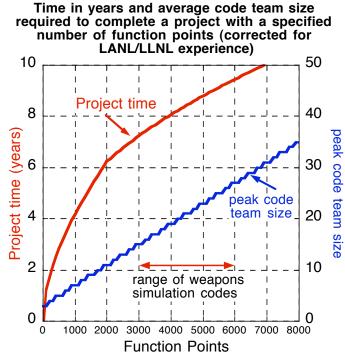

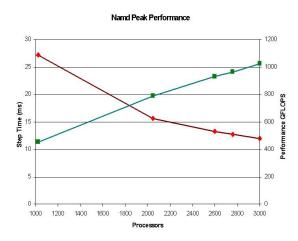

The case histories and the estimation procedures indicate that it generally takes a minimum of 8 years for a code team to develop an initial capability for a weapons code project. The requirements for a weapons code are determined by the physics necessary to simulate a nuclear weapon. LANL and LLNL have over 50 years of experience in this area, and know these requirements in detail. Weapons code projects require between 3000 and 6000 function points (Fig.2).

| Tuble 2 Software Resource Estimates for the EETTE and EATTE Code Trojects |        |        |          |                           |                            |                           |                             |

|---------------------------------------------------------------------------|--------|--------|----------|---------------------------|----------------------------|---------------------------|-----------------------------|

|                                                                           | LLNL   |        |          | LANL                      |                            |                           |                             |

|                                                                           | ASCI A | ASCI B | Legacy A | Antero<br>Code<br>Project | Shavano<br>Code<br>Project | Blanca<br>Code<br>Project | Crestone<br>Code<br>Project |

| Single Lines of Code                                                      | 184000 | 490000 | 410550   | 300000                    | 500000                     | 200000                    | 314000                      |

| Function Points (Eq.1)                                                    | 4800   | 4000   | 5400     | 2900                      | 4800                       | 3800                      | 2900                        |

| estimated schedule(Eq.4)                                                  | 8.7    | 7.6    | 6.9      | 6.6                       | 8.1                        | 7.4                       | 6.7                         |

| Project age<br>(at initial milestone date)                                | 3      | 9      | N/A      | 4                         | 3.5                        | 8                         | 8                           |

| Successful in achieving initial ASCI milestone                            | No     | Yes    | N/A      | No                        | No                         | No                        | Yes                         |

| Estimated staff<br>requirements (Eq.3)                                    | 22     | 27     | 24       | 14                        | 22                         | 18                        | 14                          |

| real team size                                                            | 20     | 22     | 8        | 17                        | 8                          | 35                        | 12                          |

Table 2 Software Resource Estimates for the LLNL and LANL Code Projects

Yellow shading indicates historical data; white background denotes computed numbers.

Figure 2. Time required to complete a project and average code team size as a function of code capability measured in Function Points[11, 12].

Some of the ASCI codes were started before ASCI began in 1996 (ASCI B, Legacy A for LLNL, and the LANL Crestone code project). ASCI B was started roughly in 1992 and had a working prototype in 1994. The Crestone code project was started before 1992. ASCI A and the Shavano and Antero code projects were started around early 1997. Legacy A was started over 30 years ago and was included for comparison. Since we are

able to match the history of weapons codes with scalings derived from the experience of the commercial software industry, we conclude that the constraints, computer science practices and management issues that generally apply to the IT industry apply to the development of weapons codes as well (i.e. there is no "Silver Bullet" that can radically reduce the development time [14]).

We found that the dominant factor for success is the age of the code project. The code projects that did not have sufficient time (8 years) to complete their projects failed to meet their milestones. All but one of the code projects that had 8 years succeeded in meeting their milestones. This is clear evidence that schedules and requirements must be consistent. The schedule cannot be fixed independently of the requirements, a fact long appreciated by the IT industry[9] but not adequately taken into account in the early planning for ASCI. Unfortunately, the ASCI program set the milestone for demonstrating the capability of each code project to be three and a half years (December 1999) after the beginning of ASCI (~mid 1996) and three years after the date (~January 1997) many of the code projects were launched. Having recently recognized this, partially as a result of our analysis, the ASCI program has revised the program milestones.

Adequate development time is necessary—but not sufficient—for success. Several code projects failed in spite of having adequate time. Poor practices and inadequate support—implicitly included in the contingency factor—hurt many of the projects as well.

A final point is that it is clear from the function point scaling relations (eqs. 1-5) that the code requirements determine both the schedule and resources needed for success. This estimating analysis indicates the importance of a realistic set of requirements, schedule and resources. Without them, projects will fail and the needed applications will not be developed.

## 4. Conclusions

Computational science has the potential to play an important role in society in many, many fields. However, if computational science is to reach the level of maturity necessary to play that role, it must increase the level of confidence in its predictions. It must develop methods to ensure that the equations and models accurately reflect the real world, that the equations and models are solved correctly, that the applications are set up and run correctly by knowledgeable and careful people, and that the results are interpreted correctly. Accurate equations and correctly implemented models requires attention to the code development process. The process must follow the general "lessons learned" discussed in the paper. Particular attention must be given to building in quality and accuracy. An intensive verification and validation program is essential. Finally, those developing the code and those using the code must have a deep appreciation of the limits of the code and a deep rooted appreciation that the results may not be correct.

## 5. Acknowledgements:

The author is grateful for discussions with Don Remer, Rob Thomsett, Tom DeMarco, Don Burton, Richard Kendall, Dale Henderson, Ken Koch, Larry Cox, Larry Votta, and Jeremy Kepner.

## 6. References

- [1] Laughlin, R., *The Physical Basis of Computability*. Computing in Science and Engineering, 2002. 4(3): p. 27-30.

- [2] Petroski, H., Design Paradigms: Case Histories of Error and Judgement in Engineering. 1994, New York: Cambridge University Press. 221.

- [3] Post, D. and R. Kendall. *Lessons Learned From* ASCI. in DOE Software Quality Forum 2003. 2003.

Washington, DC: Los Alamos National Laboratory.

- [4] Thomsett, R., *Radical Project Management*. 2002, Upper Saddle River, NJ: Prentice Hall.

- [5] Brooks, F., The Mythical Man-Month: Essays on Software Engineering, Anniversary Edition. 1995, Menlo Park: Addision-Wesley Publishing Co. 322.

- [6] Verzuh, E., *The Fast forward MBA in Project Management*. 1999: John Wiley.

- [7] DeMarco, T. and T. Lister, *Waltzing with Bears, Managing Risk on Software Projects*. 2003, New York, New York: Dorset House Publishing. 196.

- [8] Capers-Jones, T., *Estimating Software Costs*. 1998, New York: McGraw-Hill.

- [9] Yourdon, E., *Death March*. 1997, Upper Saddle River, NJ: Prentice Hall PTR.

- [10] Paulk, M., *The Capability Maturity Model*. 1994, New York: Addison-Wesley.

- [11] Jones, T.C., Estimating Software Costs. 1998, New York: McGraw-Hill. 720.

- [12] Symons, C.R., Function Point Analysis: Difficulties and Improvements. IEEE Transactions on Softwware Engineering, 1988. 14(1): p. 2-11.

- [13] Remer, D. Managing Software Projects. in UCLA Technical Management Institute. 2000. Los Angeles, CA: UCLA Extension Courses.

- [14] Brooks, F.P., No Silver Bullet: Essence and Accidents of Software Engineering. Computer, 1987.

20(4): p. 10-19.

# Application Development Productivity Challenges for High-End Computing (Extended Abstract)

Vivek Sarkar\*

Clay Williams

Kemal Ebcioğlu

#### Abstract

Application development productivity can be a significant bottleneck in the time to solution for deploying production applications on High-End Computing (HEC) systems. We discuss the fundamental reasons for these productivity barriers, and outline the solution being pursued for application development productivity in the IBM PERCS project (Productive Easy-touse Reliable Computing Systems). We also introduce a simple model for defining application development productivity, and use this model to guide our choice of solutions.

#### **1** Problem Formulation

There are multiple phases in the software lifecycle of HEC applications – algorithm development, application requirements and written specification, design/code/test of a functional implementation, porting, parallelization and tuning to obtain a scaled parallel implementation, deployment, execution and debugging of parallel implementation on a production HEC system, and feedback from production runs to earlier lifecycle phases. While some of these lifecycle phases are similar to those found in commercial applications, the HEC domain poses many unique challenges to application development productivity especially in the phases relevant to large-scale parallel implementations of HEC applications. One reason for this the fact that HEC systems exhibit large degrees of parallelism at different levels — intra-chip, intra-node and inter-node — that must be exploited to obtain production-level performance. In addition, production applications are executed on *large data sets* that increasingly stress the severe non-uniformities and discontinuities in data accesses that are present at the different levels of HEC systems due in part to the widening gap between intrachip and inter-chip data access times in both shared and distributed memory configurations. Further, each system layer — hardware, operating system, middleware, compiler, programming language — adds a layer of opacity in controlling the non-uniform data accesses supported by the hardware.

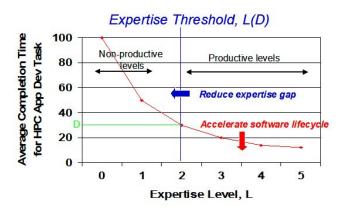

After examining why application development productivity is so low in the HEC domain, we have concluded that the two fundamental problems that need to be addressed are the Expertise Gap and the Programming Complexity, both of which are described below. The grand challenge for this area is to improve overall HEC application development productivity by  $10 \times$  by the year 2010.

1. Expertise Gap. Programming today's HEC systems requires a high level of expertise, but the current trend of available skills is increasingly one of few HEC expert programmers, and many domain scientists and software engineers who are not trained or experienced as expert HEC programmers. Only the HEC expert programmers can contribute to production-level HEC applications, thereby limiting the number of HEC solutions that can be developed. Some HEC development groups have indicated that the ratio of expert to non-expert programmers can be as low as 1 : 100 in their organizations. The HEC expert programmers are skilled in parallel programming, and have "top-gun" experience with all aspects of processor architecture, system hardware, system software, compilers, runtime systems, and parallelization/communication libraries. This level of expertise is typically acquired over a long period  $(10^+ \text{ years})$  of hands-on experience with leadingedge HEC systems. In contrast, most qualified software engineers have little or no experience with HEC systems, and usually find low-level

<sup>\*</sup>IBM T.J. Watson Research Center. Email: {vsarkar, clayw, kemal}@us.ibm.com.

parallel programming constructs (such as those in OpenMP or MPI) too complex to understand or use. Similarly, while domain scientists have an in-depth knowledge of their application domain (e.g., fluid dynamics, bio-informatics), they lack the necessary training and experience to be able to contribute to programming production HEC applications.

2. Programming Complexity. In addition to the expertise gap, tackling the non-uniformities in data access and the multiple levels of parallelism in HEC systems requires a high level of effort even from the experts who can write productionlevel HEC applications. One reason why these non-uniformities become a critical barrier to HEC application development productivity is because the programmers must be aware of discontinuities in each level of the system (L1 cache, L2 cache, L3 cache, and the interconnection networks) before they can write production-level HEC applications. In addition, the ability to translate experience with a prior HEC system to a new HEC system is very limited — it can take many months even for an expert HEC programmer to become productive on a new HEC machine. The net effect of all this programming complexity is a slower software lifecycle in HEC environments.

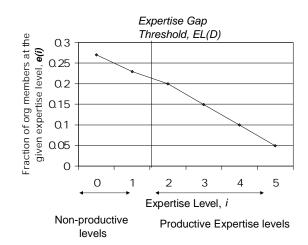

We now present a simplified *application development productivity model* to demonstrate the importance of addressing the Expertise Gap and Programming Complexity problems. Consider an average-sized organization that develops HEC applications. First, let us assume that all organization members can be grouped according into expertise levels, and that e(i) is the fraction of organization members that are at expertise level  $i \geq 0$ . e defines an expertise profile for the entire organization, and it can also be viewed as a probability density function. There are many possible definitions for expertise levels. One simple definition is as follows: an organization member is placed in expertise level i if and only if they have successfully contributed to developing i production HEC applications in their career thus far.

Next, we define  $t_S(i)$  to be the average completion time of an HEC application development task of size S by an organization member at expertise level i.  $t_S(i)$ essentially defines a learning curve or experience curve for HEC application developers in the organization. (Note that while the phrase "steep learning curve" is often used to represent a hard learning experience, it is a misnomer in this case because a steep descent in the learning curve actually represents a very successful learning experience.) In this model, we will assume that  $t_S(i)$  is monotonically non-increasing with increases in expertise level *i*. This is a statement for a given point in time — there are certainly cases when HEC technology advances introduce more software complexity over time, thereby raising  $t_S(i)$  over time for all expertise levels *i*.

The two functions, e and  $t_S$  can now be combined to obtain an application development productivity metric as follows. For simplicity, let us assume that the organization needs to complete HEC application development tasks of a fixed size S in a given duration D. In this case, productivity can be measured as the number of such tasks completed by the organization in time D. To answer this question, we can first examine the learning curve and identify the smallest expertise level EL(D)for which  $t_S(EL(D)) \leq D$ . EL(D) represents the expertise gap threshold in our model. If EL(D) > 0, it must be the case that all members with a lower expertise level than EL(D) will take longer than time D to complete a task of size S. We assume that none of the members below the expertise gap threshold can contribute towards HEC application development productivity since they will not complete their task in the assigned duration. Therefore, the productivity Pcan be expressed as

$$P = \sum_{i \ge EL(D)} \frac{e(i) \times D}{t_S(i)}$$

which is the average number of tasks of size S that can be completed (per organization member) in a given duration D. We observe that solutions to the Expertise Gap problem will lead to a smaller value of EL(D), that solutions to the Programming Complexity problem will lead to smaller values of  $t_S(i)$ , and that both sets of increases will contribute to increasing the overall productivity.

Note that the productivity discussed above differs from the standard software engineering definitions of productivity. In those definitions, productivity is in terms of the size S of the application and the effort Eit takes to develop it. The computation of size is an area of considerable debate and research in the software engineering community, with proposals ranging from lines of code to function / feature points. For an overview of productivity in software engineering, see [3]. In the traditional definition, both size and time are measured independently of the development team and their skill levels. Productivity is then defined as

$$Q = \frac{S}{E}$$

Our definition of productivity differs considerably from

Figure 1. Learning Curve for HEC Application Developers

this, as it has expertise and learning curve as its primary focus rather than size and effort. Size and effort are not absent from the measure, but are implicit. Our measure explores the effect of expertise and learning curve on productivity for applications of fixed size and projects of a fixed duration. In our approach, size could be measured using any of the techniques proposed to date. HEC applications are profoundly affected by the skills of the application development team and the complexity of the programming constructs. Because of this, we believe that our productivity model offers important insights into improving productivity for HEC application development. We plan to validate the model using data collected during as part of the PERCS project. In the remainder of this section, we illustrate this model through Figures 1 and 2.

Let us assume that we are interested in identifying the expertise levels that can contribute towards tasks of durations < 30 time units (e.g., 30 months). Figure 1 can be used to identify the expertise gap threshold, EL(D) = 2 for D = 30. Looking at where this threshold falls in Figure 2, we see that only 50% of the members can productively contribute to these tasks. Therefore, the average organizational productivity is  $P = 30 \times (0.2/30 + 0.15/20 + 0.1/14 + 0.05/12) \approx 0.76$ tasks (per organization member) completed in 30 time units. We expect to deliver productivity boosts by both lowering the Learning Curve in Figure 1, and shifting the Expertise Profile in Figure 2 to the right so as to increase the expertise level of organization members. We expect that a judicious combination of these two productivity boosts could lead to our goal of a  $10 \times$ productivity improvement by 2010.

Figure 2. Expertise Profile for HEC Application Development Organization

#### 2 Overview of our Solution

In this section, we give a high-level overview of our solutions to the Expertise Gap and Programming Complexity problems identified in Section 1.

We plan to address the Expertise Gap problem on two fronts:

1. High-level tools to make parallelism understandable by non-expert HEC programmers.

All HEC applications involve parallel programming of some kind. There has been some good progress over the last two decades on standardization of language constructs for parallel programming e.g., OpenMP, MPI, threads. However, these constructs are still too complex and lowlevel for use by non-expert programmers. We believe that higher levels of abstraction — such as data parallelism, stream parallelism, and recursive divide-and-conquer parallelism — will be more natural in making parallelism understandable by this community of programmers. Our approach will enable non-expert programmers to a) express parallelism in new HEC applications by domainspecific tools for these higher level of abstraction, and b) transform the parallel structure of the application into useful parallelism, by using a new set of tools based on analytical, simulated, and actual performance feedback.

Our infrastructure strategy for building high-level tools for HEC programmers is to extend the Eclipse tools framework (eclipse.org) with new tools and plug-ins for existing languages such as C/C++, Fortran, and Java, as well as new languages such as StreamIt, and the new parallel programming language constructs discussed later (see [6] for an example). In addition, we plan to extend the *refactoring* functionality in Eclipse to specifically simplify the task of parallelization. Refactoring is a well-known technique in the software engineering domain for providing tools that can guide programmers in performing semanticspreserving transformations, typically for improving the modular structure of a body of code. In our extensions, we will use the refactoring tools to guide non-expert programmers in correct and efficient parallelization, thereby reducing the expertise gap. One of the main research challenges is to identify and communicate performance bottlenecks at a high level to guide users in selection of transformations.

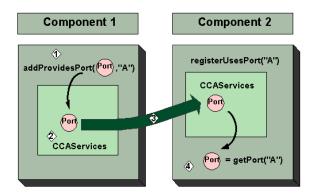

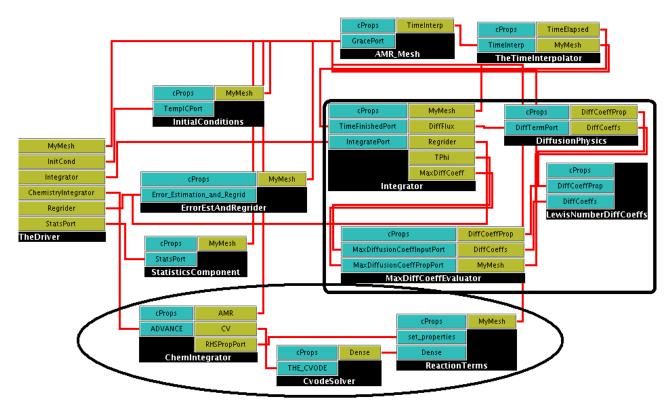

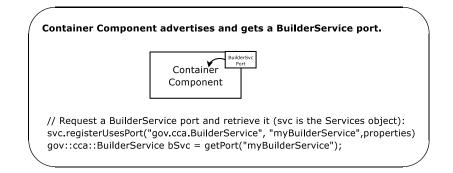

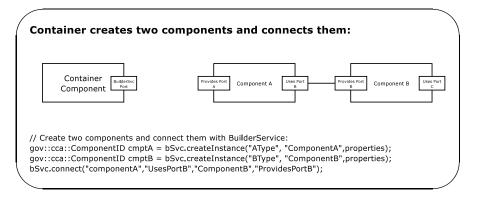

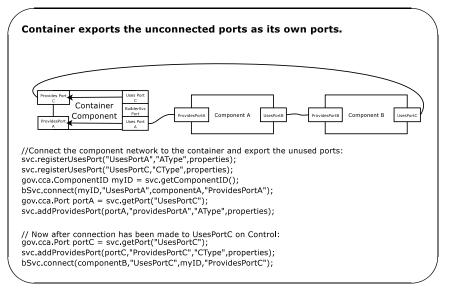

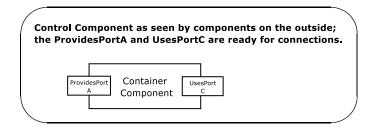

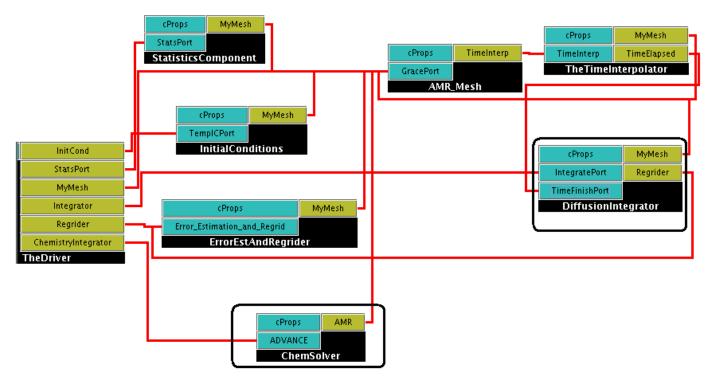

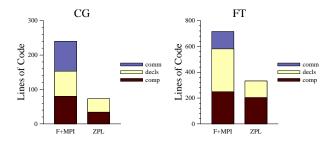

2. Leveraging component-based development in the HEC domain. It has been observed that the programming tools and practices used by the HEC community is at least a decade behind those used by developers of commercial applications. Though commercial and web applications are intrinsically concurrent and asynchronous in nature, developers of these applications are highly productive today through the use of comprehensive component and application frameworks. While the HEC community has demonstrated the ability to share numerical libraries across multiple applications, they have not as yet adapted first-class component models with strong guarantees of semantics and performance. Our implementation strategy is to leverage and extend the work under way in the CCA Forum (cca-forum.org). As components become available for reuse, they will raise the level of abstraction for building a system. When component technology matures for HEC, lower level coding will be replaced by component composition. With advanced tool support, composition is a much simpler and more uniform activity than source level coding. Thus, the level of expertise required to build HEC systems will be reduced. Furthermore, the expertise for performing certain computations can be encapsulated in components. Users of the components will only need to understand what they want to do, not the details of how to implement the computation efficiently. This also reduces the level of expertise necessary to build HEC systems. Our current plan is to select a suitable CCA framework, port it to Eclipse, and use it as the basis for research on extending CCA

to support productivity enhancements. Using Eclipse will ensure that the component work and the other Eclipse-based capabilities mentioned in this paper (refactoring, new parallel programming constructs, AOSD, etc.) will be integrated and support seamless development in the HEC tools. In the component area, a key research challenge is to deliver optimized performance akin to that of dynamically optimized libraries such FFTW, ATLAS and SPIRAL.

In addition to the Expertise Gap, we plan to address the Programming Complexity problem on three fronts:

- 1. New Programming Constructs for exploiting Parallelism and Locality in HEC systems. As discussed earlier, the learning curve for HEC applications can be formidable due to the complexity of HEC systems. The research challenge is to simplify programming of parallelism, synchronization, consistency, and object lifetimes by providing firstclass support for primitive, object, matrix and stream data types. Our proposed approach is to build the programming constructs around the following new constructs:

- (a) Enclaves, which provide static and/or dynamic grouping of objects with common properties (such as object lifetime, confinement, ownership, immutability, performance hints, etc.) and enable remote (distributed) communication of objects.

- (b) Atomic sections, which provide high level abstractions of locks without burdening the HEC programmer with details of lock management. Atomicity is a high-level property that is usually implemented by synchronization and other low-level mechanisms After determining the parallel structure of the application, the programmer may realize that some sets of statements need to be performed atomically to guarantee correct parallelization The user identifies these sets of statements as atomic sections and leaves the implementation of synchronization to the compiler and runtime system

- (c) Asynchronous operations, which provide high level abstraction of threads. By identifying an operation invocation as asynchronous, a user is logically creating a fine-grained thread for the invocation. We believe that this and similar high-level constructs will be necessary for generating the large number of threads needed for scalable performance

- (d) Safety checks to guarantee the correctness of high-level assertions such as the absence of data races [2, 5] and/or the preservation of immutability properties [4]. Extensive safety checks reduce debug and test efforts by improving software observability and diagnosability. The checks can be static or dynamic. We believe that the relative overhead of runtime safety checks will shrink as compute cycles become cheaper in 2010.

- 2. Morphogenic Software.

In much of real world software, different concerns may often be tangled together in an undesirable For example, data logging, debugging, way. accounting, and performance measurement may all be intertwined with the main calculations of a program. Aspect-Oriented Software Development (AOSD) has gained quite a bit of attention recently as a technique for reducing programming complexity by enabling *separation of concerns* [1]. However, most of the separation and composition of concerns is done at a coarse granularity such as methods or procedures. This limits its applicability to HEC applications, where one can often find a lot of complexity at finer granularities such as individual statements. We plan to address this limitation with the morphogenic software approach, which will support fine-grained extraction and composition of concerns (extension of aspectoriented programming) as well as support effective integration of heterogeneous code (C, C++, Fortran, Java, Matlab).

3. Debugging, Validation, and Verification. A key research challenge is to enable effective debugging of large-scale HEC applications with minimally invasive sampling, tracing, and instrumentation. These debugging systems will give the impression of reversible execution when needed, though this functionality will most likely be implemented by resuming execution from a prior checkpoint, and then using forward execution. The scope of the debugging agenda also includes blame analysis for functional and performance failures, validation rule-sets, domain constraints from physical systems.

### 3 Conclusions

In this paper, we outlined two fundamental problems facing HEC application developers — Expertise Gap and Programming Complexity. We proposed a simple model for measuring productivity, and briefly described how we plan to address these two problems to improve overall productivity.

#### Acknowledgments

This work has been supported in part by the Defense Advanced Research Projects Agency (DARPA) under contract No. NBCHC020056. We would like to thank all contributors to the PERCS Programming Model and Tools technical agenda outlined in this paper from IBM, and from our university partner groups at Massachusetts Institute of Technology, Purdue University, University of California at Berkeley, University of Delaware, University of Illinois, University of Texas at Austin, and Vanderbilt University.

#### References

- Special issue of Communications of the ACM on Aspect-Oriented Programming. October 2001, Volume 44, Number 10.

- [2] J.-D. Choi, K. Lee, A. Loginov, R. O'Callahan, V. Sarkar, and M. Sridharan. Efficient and precise datarace detection for multithreaded object-oriented programs. In SIGPLAN '02 Conference on Programming Language Design and Implementation, June 2002.

- [3] N. E. Fenton and S. L. Pfleeger. Software Metrics: A Rigorous and Practical Approach. PWS Publishing, second edition, 1997.

- [4] I. Pechtchanski and V. Sarkar. Immutability Specification and its Applications. Concurrency and Computation Practice & Experience (CCPE), 2003.

- [5] M. Prvulovic and J. Torrellas. ReEnact: Using Thread-Level Speculation to Debug Software; An Application to Data Races in Multithreaded Codes. In Proceedings of the 30th Annual International Symposium on Computer Architecture (ISCA), June 2003.

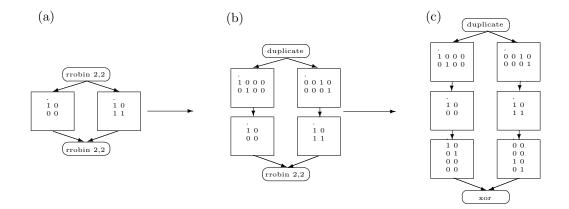

- [6] A. Solar-Lezama and R. Bodik. Templating Transformations for Bitstream Programs. In Proceedings of the HPCA Workshop on Productivity and Performance in High-End Computing (P-PHEC), February 2004.

# **Comparing Network Processor Programming Environments: A Case Study**

Niraj Shah, William Plishker, Kurt Keutzer University of California, Berkeley {niraj,plishker,keutzer}@eecs.berkeley.edu

#### Abstract

Network processors have emerged as prominent examples of multiprocessor application-specific programmable architectures. While there have been significant architectural developments in this field, widespread adoption will be predicated on productively programming high performance applications on these architectures. This paper presents a case study of two programming environments for a common network processor, the Intel IXP1200. We compare the development process, achievable performance, and resource usage of the final implementations using these two programming approaches and draw conclusions regarding the advantages and disadvantages of these approaches.

#### 1. Introduction

The costly unpredictable nature of ASIC design coupled with increased silicon capability is fueling the rise of multi-processor application-specific architectures. Examples of this trend have already been demonstrated in networking, multimedia, and graphics. Architectures for these application-specific programmable processors have been explored in great depth. For example, current network processors share many of the complex architectural features of traditional high-performance computing systems: multiple processing elements each with multiple hardwaresupported threads, distributed memories, specialpurpose hardware, and a variety of communication mechanisms.

Despite the deep architectural emphasis, there has been relatively modest investigation of their programming environments. For many system designers who chose to use these programmable solutions, their success will depend largely on their ability to implement a high-performance application in a short (or at least predictable) design time. Current options for programming network processors are: assembly language, C language variants [1] [2] [3], and block-based frameworks [4] [5]. The most common approach is to use assembler or a subset of C with architecture specific extensions (e.g. Intel Microengine C [1], Motorola's C-Ware [2], Teja Technologies Teja C [3]). In addition, a few efforts have raised the programming abstraction to a higher level. For example, Intel has released a framework called ACE [4] that is a librarybased approach built on assembly code. Another such effort, NP-Click [5], combines Click [6], a popular networking specification language, with an abstraction of the target network processor architecture.

This paper is a case study comparing two different software development approaches for a representative network processor, the Intel IXP1200 [7]: Microengine C (which we refer to as IXP-C) and NP-Click. We chose these two software development approaches to compare different levels of abstraction: a C-like language and a domain-specific language. To our knowledge, this is the first research effort to compare in a detailed manner the software development methodologies for a network processor. We chose the IXP1200 over newer architectures based on the availability of software development environments. However, we believe the results of this study are applicable to recently released architectures like the Intel IXP2xxx family as well as other network processor families.

To compare these two programming approaches, we use each of them to implement a 16 port IPv4 packet forwarder and a 4 port Differentiated Services (DiffServ) interior node. The IPv4 packet forwarder is a performance focused benchmark, while the DiffServ application contains more functionality, but supports fewer ports. We compare these two software development approaches across three categories: development process, achievable performance, and resource usage of the final implementation. We analyze these results and compare and contrast the advantages and disadvantages of the IXP-C and NP-Click programming environments.

The remainder of this paper is organized as follows: Section 2 provides a brief architectural description of the Intel IXP1200. Section 3 describes the two software development approaches we chose: IXP-C and NP-Click. Section 4 describes the applications we implemented: IPv4 packet forwarding and a DiffServ interior node. Results are presented in Section 5. Finally, sections 6 and 7 summarize our results and comment on future work, respectively.

#### 2. Intel IXP1200

For this case study we chose the Intel IXP1200 because it is representative of other network processing and other multi-processor application-specific architectures. In addition, the IXP1200 has numerous available programming environments, relative to other network processors.

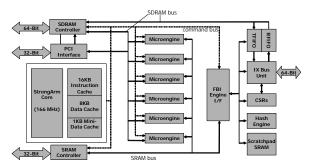

The IXP1200 is one of Intel's first network processors based on their Internet Exchange Architecture. It has six identical RISC processors, called microengines, plus a StrongARM processor. The StrongARM is used mostly to handle control and management plane operations. The microengines are geared for data plane processing and each has hardware support for four threads that share a fixed size program memory. The memory architecture is divided into several regions: large off-chip SDRAM, faster external SRAM, internal Scratchpad, and local register files for each microengine. Each of these areas is under the direct control of the user and there is no hardware support for caching data from slower memory into smaller faster memory (except for the small cache accessible only to the StrongARM). There is also a hash engine coprocessor that provides hardware support for hash key creation. The IX Bus (an Intel proprietary bus) is the main interface for receiving and transmitting data with external devices such as Ethernet MACs and other IXP1200s. It is 64 bits wide and runs up to 104MHz allowing for a maximum throughput of 6.6Gbps. The microengines can directly interact with the IX bus, so any microengine thread may receive or transmit data on any port without StrongARM intervention. This interaction is performed via Transmit and Receive FIFOs which are circular buffers that allow data trans-

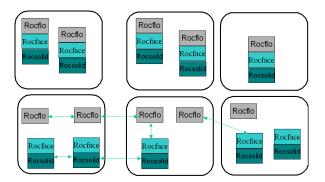

Figure 1. Intel IXP1200 microarchitecture

fers directly to/from SDRAM. For the microengines to interact with peripherals (e.g. determining their state), they need to query or write to Control Status Registers (CSRs). Accessing control status registers requires using the Command Bus which doubles as the interface to the hash engine, scratchpad memory, and Transmit and Receive FIFOs. A micro-architectural diagram of the Intel IXP1200 is show in Figure 1.

#### **3.** Software Development Approaches

For this case study, we focus on software development for data-plane processing, where high throughput and low latency are required. In this section we describe the two IXP1200 microengine software development approaches we chose to compare: IXP-C and NP-Click.

#### 3.1. Intel IXP1200 Microengine C (IXP-C)

The initial programming model that Intel provided for the microengines was assembly language [8]. This is the lowest level of programming the architecture as it exposes all facets of the architecture under programmer control. Intel also provided a macro assembler that supports higher-level programming constructs like conditionals and loops. There is also a register allocater so symbolic variable names can be used.

Later, Intel augmented their assembly language interface to the microengines with a subset of C (which we refer to as IXP-C) [1]. IXP-C supports loops, conditionals, functions, intrinsics (function calls using C syntax that direct instruction selection), basic data types, and abstract data types such as structs and bitfields. However, data allocation to different memory regions is user defined; for practical applications, explicit binding is necessary at declaration time. In addition, the multithreading model is explicit: the programmer must manually divide their application across microengines and threads, control all inter-processor and thread communication, and arbitrate access to shared resources. Intel also provides a library that defines additional data types, macros, and functions that provide a slightly higher abstraction of the hardware. For example, there are bit-fields that export the format of control status registers and intrinsics for assembler instructions that use the hash engine.

#### 3.2. NP-Click

NP-Click [5] is a programming model implemented for the Intel IXP1200 that combines the "flow-based router" concept from Click [6] with an abstraction of the target architecture. Like Click, *elements* are the base unit of computation in NP-Click. Elements correspond to common networking operations like classification, route table lookup, and header verification. Elements communicate by passing packets using well-defined semantics. There are two types of communication: push and pull. Push communication is initiated by the source element and effectively models the arrival of packets into the system. Pull communication is initiated by the sink element and often models available memory in hardware resources for egress packet flow. In NP-Click, the elements are implemented in IXP-C to leverage the existing compiler for the IXP1200.

NP-Click also provides visibility into salient architectural details that greatly affect performance. Specifically, it enables programmers to:

- control thread boundaries to effectively manage processor and thread utilization

- map data to different memories (registers, Scratchpad, SRAM, and SDRAM)

- separate design concerns of arbitration of shared resources and functionality

NP-Click separates the application description from implementation choices, such as functional partitioning across microengines or arbitration schemes for shared resources. For example, after initially implementing their application in NP-Click, the application programmer is able to change the thread boundaries to try different implementations without changing the application description.

#### 4. Applications

For this case study, we use IXP-C and NP-Click to implement two applications: packet forwarding and a DiffServ interior node. The IPv4 packet forwarding application is a performance-centric benchmark with relatively narrow functionality. The second application, a DiffServ interior node, is a functionally rich application with lower performance requirements.

#### 4.1. IPv4 Packet Forwarding

IP Version 4 packet forwarding [9] is a common kernel of many network processor applications. We chose to implement the data plane of a 16 port Fast Ethernet (16x100Mbps) IPv4 router. The major features of this benchmark are listed below:

• incoming packets are checked for validity, including proper version number and correct header length

- the egress port of a packet is determined by a longest prefix match route table lookup based on the IPv4 destination address field

- after the egress port has been determined, the time-to-live (TTL) and checksum fields in the packet header are updated

#### 4.2. Differentiated Services Interior Node

The differentiated services architecture (DiffServ) [10] is a method of facilitating end-to-end quality of service (QoS) over an existing IP network. In contrast to other QoS methodologies, it is a provisioned model, not a signaled one. This implies network resources are provisioned for broad categories of traffic instead of employing signaling mechanisms to temporarily reserve network resources per flow. A DiffServ network relies on traffic conditioning at the boundary nodes to simplify the job of the interior nodes. The boundary nodes of a DiffServ network aggregate ingress traffic into a number of categories, called behavior aggregates (BAs), using the differentiated services codepoint (DSCP) as specified in [11]. The interior nodes apply different per hop behaviors (PHBs) to each of the BAs. The classes of PHBs recommended by IETF include:

- Expedited Forwarding (EF): low packet loss, latency and jitter

- Assured Forwarding (AF): 4 classes of traffic, each with varying degrees of packet loss, latency and jitter

- Best Effort (BE): no guarantees of packet loss, latency, or jitter

The PHBs in a DiffServ implementation are defined by a combination of:

- classifiers: elements that select a subset of the packet stream based on packet header fields

- traffic conditioners: elements that measure, mark, shape and drop packets

For this case study, we implemented an interior DiffServ node. While there is less monitoring and shaping than in a boundary node, we believe an interior DiffServ node is a good benchmark for network processors as it is a functionally rich application that stresses different aspects of the development process.

Our DiffServ application begins with data-plane IPv4 packet forwarding functionality. After an ingress packet passes through IP verification, IP lookup, and time-to-live decrement, it is classified based on its DSCP, with each class of traffic receiving different treatment. For example, EF traffic is first metered, with traffic below the specified data rate queued for transmit, while traffic above this data rate is discarded. On egress, we use two cascaded packet schedulers:

- deficit round-robin scheduling (DRR) [12] for EF and AF classes with a weighting toward EF and higher priority AF classes

- strict priority scheduling between the output of DRR scheduling and BE traffic

The DiffServ application we implement supports 4 Fast Ethernet ports (4x100Mbps). Though the IXP1200 may seem like overkill for this application, we attempted to implement an 8x100Mbps version of this application, but neither the IXP-C nor NP-Click implementation could support this line rate.

#### 5. Results

To test each implementation, we used a cycleaccurate architecture simulator of the IXP1200 [13] assuming a microengine clock rate of 200MHz and an IX Bus clock rate of 100MHz. Our simulation environment also models the Ethernet MACs (Intel IXF440s) connected to the IX Bus. For both applications, the destinations of the input packet streams were randomly distributed evenly across the output ports. In addition, the routing table contained 1000 entries and measurements were not taken until steady state was reached.

#### 5.1. Performance

This section describes the measurement methodology and performance results of the IXP-C and NP-Click implementations. We first present the results for IPv4 packet forwarding, then for the DiffServ interior node.

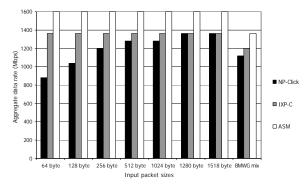

**5.1.1. IPv4 Packet Forwarding.** To measure performance for the IPv4 packet forwarding application, we consider the packet forwarder to be functional if it

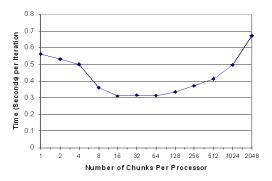

Figure 2. Performance comparison of 16 port IPv4 packet forwarding implementations

has a steady state transmit rate that is within 1% of the receive rate without dropping any packets. We test each of the implementations with a variety of single packet size input streams (64, 128, 256, 512, 1024, 1280, and 1518 bytes) and the IETF Benchmarking Methodology Workgroup (BMWG) mix [14]. We use 64 and 1518 byte packet streams as they represent the minimum and maximum frame sizes permitted by the Ethernet standard. The packet sizes in between are included to give additional insight into the performance of the different implementations. The BMWG packet mix provides a more realistic input data set as it contains an even random distribution of seven packet sizes ranging from 64 bytes to 1518 bytes. For each input packet stream, we measure the maximum sustainable aggregate data rate.

The results of our experiments for IPv4 packet forwarding are shown in Figure 2. The IXP-C implementation is able to perform at 85% of line rate (1360Mbps aggregate) across all single packet size input streams. For the BMWG packet mix, the performance is slightly lower (1200Mbps aggregate) because of dynamic load balancing effects. We attribute the consistent data rate across all packet sizes to suboptimal arbitration of multiple threads accessing the shared transmit FIFO as the performance limiting factor.

The aggregate bandwidth of the NP-Click implementation ranges from 880-1360Mbps. NP-Click's implementation has more processing overhead per packet than IXP-C's. As a result, for data streams composed of smaller packets, NP-Click's throughput suffers. For the BMWG packet mix, a more realistic data set, the NP-Click version also suffers from load balancing issues, but is able to achieve 93% of the IXP-C implementation (1120Mbps aggregate).

For reference, we show the performance of a handtuned assembler implementation based on an Intel reference design. The assembler implementation was able to meet line rate (1600Mbps aggregate) for single packet size streams, but only maintains 1360Mbps when tested with the BMWG packet mix. Both the IXP-C and NP-Click implementations fall short of this, by 11.7% and 17.6% respectively, because of the fine degree of scheduling that is available only when programming at the assembly language level.

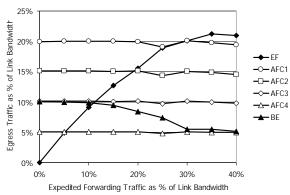

**5.1.2. Differentiated Services Interior Node.** For the DiffServ application, measuring performance is not as simple since the specification requires non-conforming packets to be dropped. Thus, the transmit data rate will always be less than received data rate. To gauge performance we compare the egress data rates of the constituent traffic flows. For the baseline setup for all

measurements, the ingress data rates were set to the following percentages of ingress bandwidth: